Giảm wafer là một bước quan trọng trong sản xuất chất bán dẫn, và mục đích chính của nó là đáp ứng các yêu cầu về hiệu suất chip, bao bì, tản nhiệt, v.v.

Mục lục

Độ dày của wafer silicon

Ưu điểm sau khi wafer mỏng

Quy trình mỏng wafer

Công nghệ mỏng wafer

1. Độ dày wafer silicon

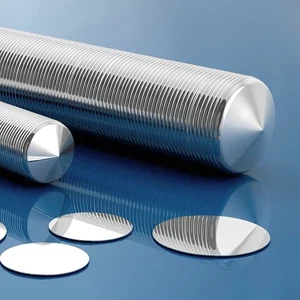

Trong quá trình đầu tiên của sản xuất chất bán dẫn, wafer cần có đủ độ dày để đáp ứng các yêu cầu về sức mạnh cơ học và độ cong vênh để có thể xử lý và chuyển giao trong và giữa các thiết bị.

150mm (6- inch) wafer

Độ dày tiêu chuẩn: Khoảng 675 micron

Phạm vi: Thường là từ 650 micron đến 700 micron

200mm (8- inch) wafer

Độ dày tiêu chuẩn: Khoảng 725 micron

Phạm vi: Thường là từ 700 micron đến 750 micron

300mm (12- inch) wafer

Độ dày tiêu chuẩn: Khoảng 775 micron

Phạm vi: Thường là từ 750 micron đến 800 micron

2. Ưu điểm của wafer mỏng

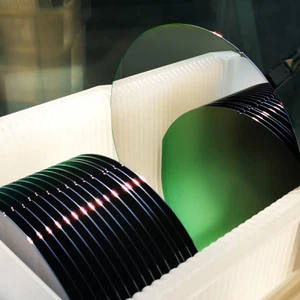

Trong giai đoạn đóng gói, để đáp ứng các yêu cầu của quy trình bao bì, wafer thường cần được mỏng đến khoảng 100 ~ 200 micron. Điều này là do wafer mỏng có thể mang lại những lợi thế sau:

Giảm khối lượng gói: Tấm vải mỏng hơn giúp đạt được sự thu nhỏ của bao bì chip

Cải thiện hiệu quả tản nhiệt: Các tấm vải mỏng có lợi hơn khi chiết nhiệt từ chất nền

Giảm căng thẳng bên trong: Làm mỏng có thể làm giảm căng thẳng bên trong được tạo ra trong quá trình hoạt động của chip, do đó làm giảm nguy cơ nứt chip

Cải thiện hiệu suất điện: Các tấm vải mỏng có thể làm cho lớp mạ vàng phía sau gần hơn với mặt phẳng mặt đất, do đó tối ưu hóa hiệu suất tần số cao

Cải thiện năng suất giảm giá: Các tấm vải mỏng có thể làm giảm khối lượng xử lý trong quá trình cắt đủ gói và tránh các khiếm khuyết như sụp đổ cạnh và sụp đổ góc

3. Quá trình mỏng wafer

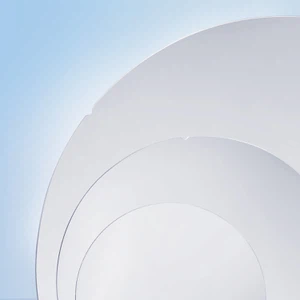

Để đạt được độ mỏng wafer, mài cơ học, đánh bóng cơ học hóa học (CMP) và các quá trình khác thường được sử dụng.

Quá trình cụ thể của quá trình mỏng bao gồm chuẩn bị sơ bộ, hoạt động mỏng (như mài thô, mài mịn, đánh bóng, v.v.) và xử lý hậu kỳ (như loại bỏ dư lượng, đo độ phẳng, kiểm tra chất lượng, v.v.).

Trong các công nghệ đóng gói nâng cao như bao bì 2.5D và 3D, độ dày chip cần thiết thậm chí có thể thấp tới 30 micron

4. Công nghệ mỏng wafer

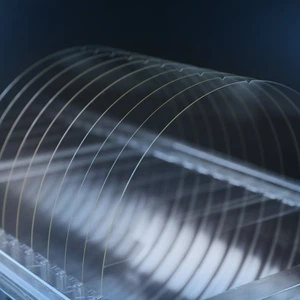

1. Phương pháp mài cơ học

Nghiền cơ học là một trong những phương pháp mỏng wafer được sử dụng phổ biến nhất, loại bỏ vật liệu dư thừa ở mặt sau của wafer bằng ma sát vật lý. Phương pháp này thường được chia thành hai giai đoạn: mài thô và mài mịn:

Nghiền thô: Sử dụng bánh xe nghiền kim cương hoặc nhựa để loại bỏ một lượng lớn vật liệu ở tốc độ cao

Nghiền mịn: Sử dụng chất mài mòn mịn hơn và tốc độ mài thấp hơn để tiếp tục tinh chỉnh bề mặt wafer và giảm độ nhám. Ưu điểm của mài cơ học là hiệu quả và tốc độ cao, phù hợp để sản xuất hàng loạt, nhưng có thể gây ra căng thẳng cơ học và thiệt hại bề mặt.

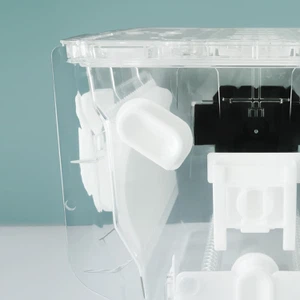

2. Đánh bóng cơ học hóa học (CMP)

CMP kết hợp các tác động kép của khắc hóa học và mài cơ học. Thông qua hiệu ứng hiệp đồng của bùn hóa học và pad đánh bóng, nó loại bỏ hình thái không đều trên bề mặt wafer và đạt được hóa phẳng cao. CMP có thể cung cấp độ chính xác và chất lượng bề mặt kiểm soát cao hơn, và phù hợp cho sản xuất mạch tích hợp với các yêu cầu chất lượng bề mặt cực cao.

3. Khắc ướt

Etching ướt sử dụng hóa chất lỏng hoặc khắc để loại bỏ các lớp vật liệu cụ thể trên wafer thông qua các phản ứng hóa học. Nó được chia thành khắc đẳng hướng và khắc dị hướng. Ưu điểm của việc khắc ướt là khả năng chọn lọc cao và khả năng kiểm soát tốt, có thể đạt được độ chính xác xử lý cấp nano trên bề mặt wafer.

4. Khắc khô

Khắc khô sử dụng dầm plasma hoặc ion để loại bỏ vật liệu, và có các đặc điểm của độ chính xác cao và độ chọn lọc cao. Nó phù hợp cho việc mỏng wafer đòi hỏi các cấu trúc độ chính xác và phức tạp cao.

5. Laser mỏng

Công nghệ mỏng laser sử dụng mật độ năng lượng cao của chùm tia laser để loại bỏ vật liệu thông qua hành động nhiệt hoặc quang hóa. Phương pháp này có thể đạt được độ mỏng cục bộ và phù hợp để xử lý tốt các khu vực cụ thể.